| Pin | Name | Func DS old |

| 1 | SSC1 | |

| 2 | asc1 | |

| 3 | 0v | |

| 4 | not used | |

| 5 | PS1 | |

| 6 | REV1 | |

| 7 | 0v | |

| 8 | LDR5 | |

| 9 | LDR4 | |

| 10 | LDR3 | |

| 11 | LDR2 | |

| 12 | LDR1 | |

| 13 | LDR0 | |

| 14 | LS1 | |

| 15 | 0v - check | Power ( thick track on flex) |

| 16 | DISP0 | |

| 17 | DPL1 | |

| 18 | DCLK1 | |

| 19 | 0v | |

| 20 | LDG5 | |

| 21 | LDG4 | |

| 22 | LDG3 | |

| 23 | LDG2 | |

| 24 | LDG1 | |

| 25 | LDG0 |

|

| 26 | LDB5 | |

| 27 | LDB4 | |

| 28 | LDB3 | |

| 29 | LDB2 | |

| 30 | LDB1 | |

| 31 | LDB0 | |

| 32 | GCK1 | |

| 33 | GSP1 | |

| 34 | ?shorted to gnd> | |

| 35 | MOD1 | |

| 36 | 0v | |

| 37 | (C15) 5uf | |

| 38 | power c94 | |

| 39 | COM1 | |

| 40 | 0v | |

| 41 | cl4 | power |

| 42 | cl15 | power |

| 43 | 0v | |

| 44 | vdd-5 | power |

| 45 | VDD-10 | power |

| Backlight Vf~13V, -ve nearest edge of LCD | ||

DS Lite

| 1 | ||

| 2 | VDD10 | +10V |

| 3 | pwr | +5V |

| 4 | 0v | |

| 5 | pwr | +3.3V |

| 6 | mod | ?mode? hi on lower disp, lo on upper |

| 7 | gsp | frame sync |

| 8 | gck | |

| 9 | B0 | |

| 10 | B1 | |

| 11 | B2 | |

| 12 | B3 | |

| 13 | B4 | |

| 14 | B5 | |

| 15 | G0 | |

| 16 | G1 | |

| 17 | G2 | |

| 18 | 0v | |

| 19 | G3 | |

| 20 | G4 | |

| 21 | G5 | |

| 22 | R0 | |

| 23 | R1 | |

| 24 | R2 | |

| 25 | R3 | |

| 26 | R4 | |

| 27 | R5 | |

| 28 | 0v | |

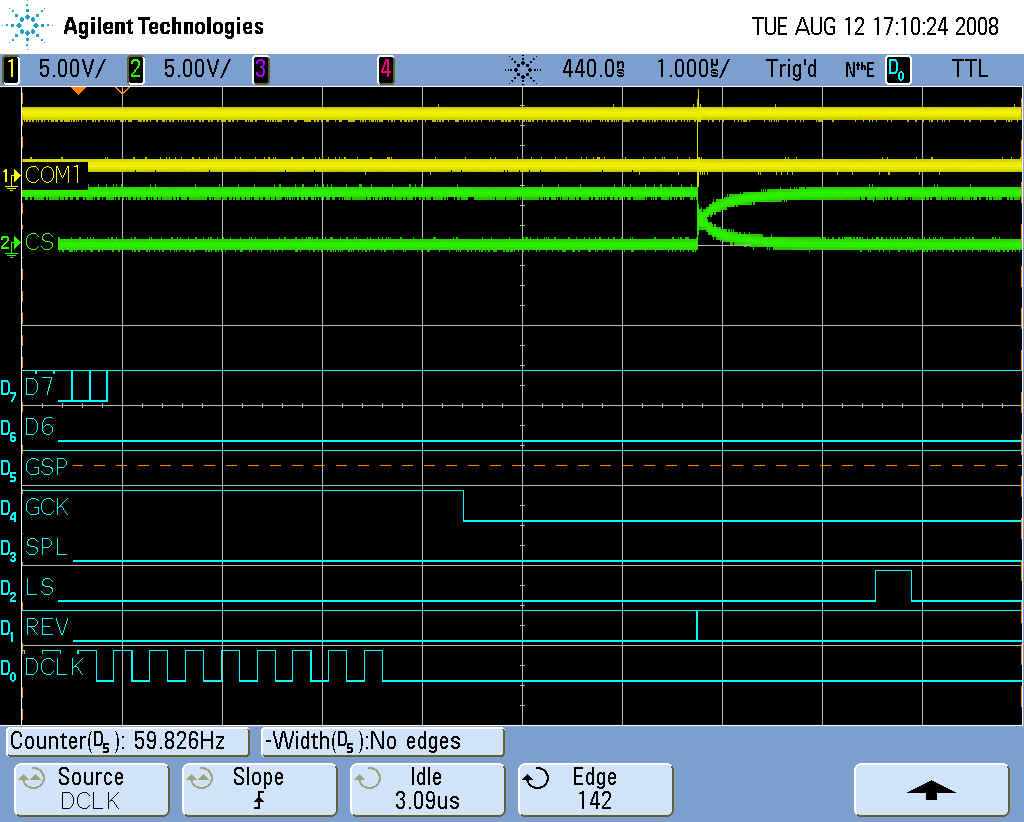

| 29 | dclk | 2.8MHz clock. 150 clocks/line, 10uS gap data clocked on both edges |

| 30 | spl | Start pixel line |

| 31 | ls | Line start ( source driver latch?) |

| 32 | pwr | +3.3v |

| 33 | 0v | |

| 34 | "comx" | in phase with com, 0/+3v2. may be drive - spiky |

| 35 | rev | Logic-level version of COM |

| 36 | 0v | |

| 37 | com1 | Bipolar, alternates on line and frame. +1.7V, -1.5V. offset sets contrast |

| 38 | leda1 | +11v4 |

| 39 | (33R to 0V) bl -

|

0v2 |

|

|

Horiz